|

|

|

|

|

|

美隆電子有限公司 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

期日: |

2007年4月11日 |

|

|

|

|

|

|

|

降低I/O設計功率 業界制訂低功耗新標準 |

|

|

|

|

|

|

|

|

|

|

|

|

Rambus公司以及一些領先的學術機構即將為功耗設定一個高水位(high-water

mark)的標準,以便能將快速的晶片至晶片間 |

|

互連帶入一個低功耗設計的新紀元。同時,此舉也有助於向業界提出了一個新課題─必須重新審視在互連設計中定義、測 |

|

|

量與建置功率的基本假設方式。 |

|

|

|

在日前舉行的國際固態電路大會(ISSCC)上,Rambus描述了一款採用90nm製程技術所製造的6Gbps串列/解串列(serdes)收 |

|

|

發器,該元件的功耗僅為2.2mW/Gbit/s。而當今的設計所需的處理器功耗大約是該元件功耗的10倍以上。 |

|

|

|

此外,TI也在ISSCC大會上發佈一款以65nm製程技術製造的12.5Gbps串列解串列器,其功耗為27.5mW/Gbit/s。Sony則發 |

|

|

表一篇論文,介紹一款採用90nm技術製造的10Gbps收發器,功耗約為25mW/Gbit/s。 |

|

|

|

|

|

相形之下,Rambus目前旗下的現有產品功耗均高。Rambus的XDR和FlexIO兩種互連產品的功耗都約為20mW/Gbit/s。 |

|

|

|

|

|

為了因應此發展趨勢,英特爾的工程師在‘IEEE電路設計大會’上發表了一篇論文,它提出了可實現10mW/Gbit/s低功耗的設 |

|

計途徑。目前採用PCI

Express連接的主流PC典型輸入/輸出功耗範圍約在15∼30mW/Gbit/s之間。 |

|

|

|

Rambus公司高層並未說明該公司何時或如何將該技術投入市場,但他們明確表示,在其發展前進的道路上並沒有什麼重大 |

|

的阻礙。 |

|

|

|

測試晶片結果出乎意料的好,我們對此感到興奮,”Rambus的首席科學家Mark Horowitz表示。他同時也是Rambus的創辦人 |

|

之一,以及該論文的共同作者。“對於許多論文而言,你都必須虔誠地祈禱它能名副其實。但我們的論文不會這樣;儘管目 |

|

前仍存在著耐用性和和量產方面的爭議,但我對此並不擔心。”Horowitz同時也是史丹佛大學的電腦科學與電子工程學教授。 |

|

|

事實上,該技術也許可為Rambus帶來更多主流的機會,而非僅該公司所熟悉的高階、強調由速度驅動的互連產品。 |

|

|

|

這是針對大量的電腦和消費應用所設計的,”Rambus公司工程部門的資深副總裁Kevin Donnelly表示。在Rambus所進行的 |

|

|

另一項計劃達到同樣2.2mW/Gbit/s功耗的專案,採用了65nm技術,但其性能則可提高4倍。“下一代技術的功耗預算必須與 |

|

原有技術的功耗預算相當,”Donnelly表示。 |

|

|

|

實際上,Rambus希望能夠建立1mW/Gbit/s這樣的指標,以作為衡量I/O功耗的金科玉律,就如同Mips/W已經廣泛地取代了 |

|

|

MHz,成為微處理器的主要衡量標準一樣。 |

|

|

|

除了重新設定低功耗serdes設計的限制以外,該論文並對電子產業傳達了一項訊息:在各種互連標準中寫入1V的訊號傳輸 |

|

|

已不被接受了。Rambus團隊利用低於200mV的傳輸訊號率已為低功耗互連推動了一項新標準。 |

|

|

|

工程師們必須對研發團隊用來搭建可處理低電壓訊號傳輸的接收器等各種技術作好準備。這些技術包括:積極地將邏輯功 |

|

|

能推向軟體、將自適應訊號等化作用的重心從發射器移至接收器端等。 |

|

|

|

如上所述的一種展示將改變人們對於哪些是可能及不可能的看法,”Horowitz表示。“如果將訊號傳輸標準設定為1V,那就無 |

|

法實現低功耗I/O。” |

|

|

|

人們之所以需要1V擺幅的原因是由於無法實現更好的接收器。其實,它必須採用更複雜且先進的技術,”該論文的另一作者 |

|

、同時也是史丹佛大學電腦科學系系主任Bill Dally表示。 |

|

|

|

隨著高階微處理器開始需要高達Tbit/s的I/O,低功耗晶片間的互連正迅速成為一項必要條件。“我們必須面對挑戰並採取行動 |

|

,否則當未來晶片接腳數以百千計出現時,I/O功耗將主宰整個系統,”一位資深工程師表示。“而目前所開發的大部份高 |

|

階晶片都受制於功耗,” Horowitz表示。 |

|

|

|

雖然在論文發表前,ISSCC嚴密封鎖該論文的相關細節,但已經有一些研究人員對Rambus的成果頗有微詞。“對於Rambus |

|

|

來說也許是一項突破,但它尚難成為先進的技術,”在《EE

Times》專門探討互連技術的部落格上,一篇匿名的留言作了以 |

|

上的評論。該留言並提到由三星電子和UCLA在2004年發表的一篇論文,文中指出用晶片電容耦合方法可實現Gbit/s訊號傳輸 |

|

系統,該系統採用100nm製程技術而功耗僅1.92mW/Gbit/s。 |

|

|

|

同樣在ISSCC大會上,來自UCLA的其他研究人員發表結合兩種RF技術與電容器耦合所開發的一款10Gbps/pin(每接腳 |

|

|

10Gbit/s)互連;該產品採用180nm技術製造,並實現了低至2.7mW/pin功耗的超寬頻連接。該設計主要針對晶片3D堆疊內的 |

|

|

晶粒連接。 |

|

|

|

昇陽電腦(Sun

Microsystems)公司至少在這三年來持續研發一種用於晶片間互連的電容耦合技術。昇陽的Proximity技術曾與 |

|

其致力於獲得一項政府的超級運算專案有關,但Sun卻在去年底失去了這個機會。當時,昇陽公司主管表示仍將繼續推動該 |

|

技術的研發。Proximity技術據稱可比目前的BGA封裝提供多達100倍的連接。 |

|

|

|

|

|

|

|

|

|

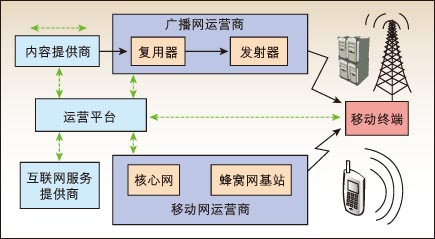

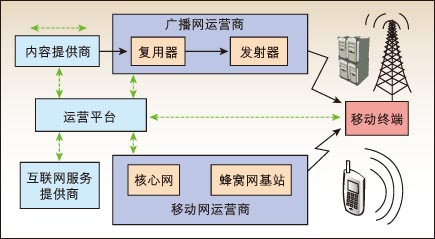

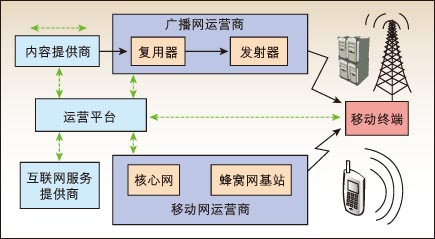

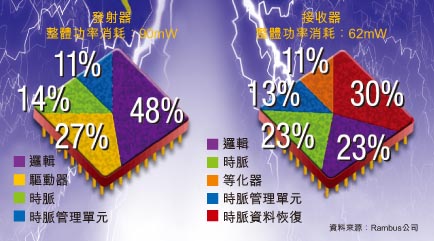

圖:業界必須重新思考功耗在互連設計中的定義。 |

|

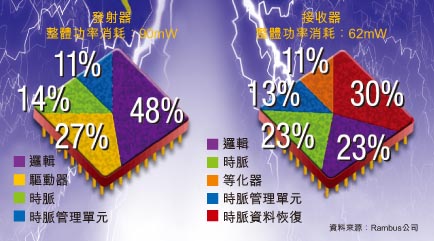

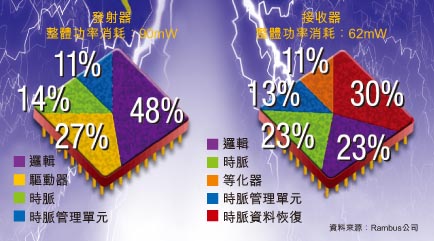

圖3:功耗何去何從?對典型串列解串列收發器的概略分析顯示,功率 |

|

耗散廣泛分佈於不同的元件中。 |

|

|

|

|

|

|

|

|

|

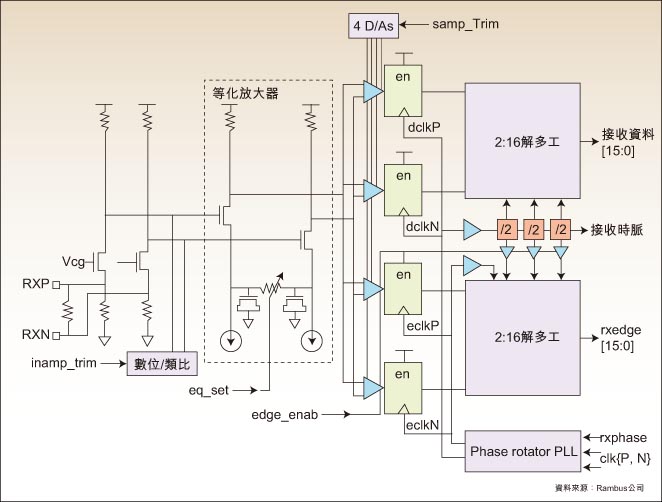

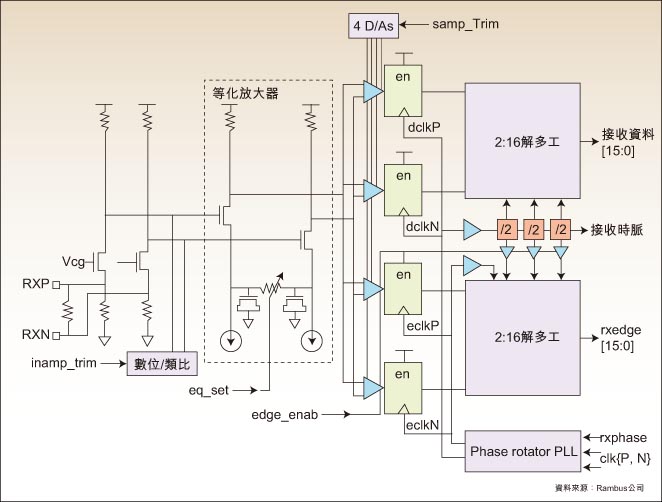

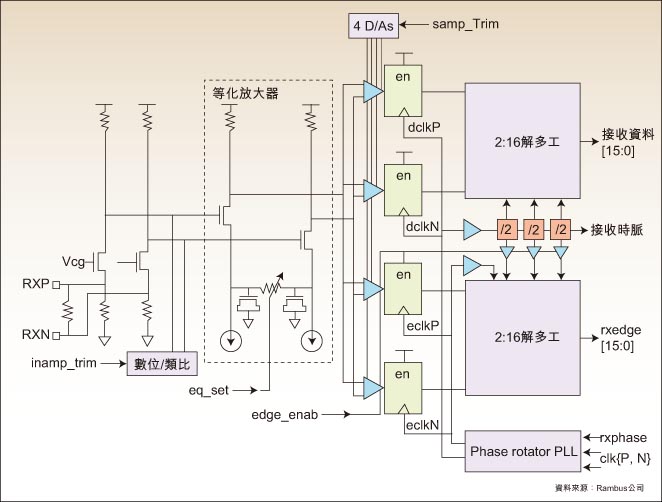

圖4:軟體處理和邏輯重用使Rambus不需使用內插器模組,並使硬體預算持續降低。 |

|

|

|

如何實踐? |

|

|

Rambus的作法是採用了各種技術組合以實現其2.2mW/Gbit/s的里程碑,其中包括由UCLA研究員Ken Yang所開發的一種電 |

|

壓模式傳輸技術。“你無法僅就單方面的努力而達到降低整體功耗的目的,”Horowitz說。“而是必須在邏輯、時脈、訊號 |

|

傳輸以及基礎發射器和接收器方面都尋求創新。我們在某些方面已建立合作模式,但在其他方面就只能靠自己了。” |

|

|

|

目前所實現的兩項較大創新成果:一是將自適應等化作用的重心從發射器轉向接收器端,另一項則是將基本微控制器上更多 |

|

的等化作用從專用硬體推移到軟體中。“在實現一款極為敏感的接收器後,如果從接收器的那一端開始運作並一路回推,那 |

|

麼便能從整個系統的功耗降低中受益,”該論文的共同作者、同時也是北卡羅萊納州大學Chapel

Hill分校電腦科學系教授 |

|

|

John Poulton表示。 |

|

|

|

研究人員們並找到了一種可利用取自時脈資料恢復(CDR)單元的現有資訊,以測試訊號高頻損失,並在接收器內透過有效產 |

|

生Dally所謂‘三重旋鈕’補償的建置方法。 |

|

|

|

在系統時脈快或慢時的CDR資料“提供了有關訊號眼圖是張開或是關閉的確切資訊,”該論文的主要作者Robert Palmer表示。 |

|

在掌握這些資料並明智利用其他現有模組後,便不再需要典型接收器中所使用的振盪器和內插器(interpolator)邏輯了。 |

|

|

|

過去缺乏額外的硬體來處理自適應等化作用,”Palmer表示。“在一般的設計中,內插器邏輯所使用的功率幾乎與整個鏈路一 |

|

樣多,”Dally說。因此,接收器所產生的靈敏度可使工程師透過一般用於高速串列解串列器在發送階段所採用的硬體FIR濾 |

|

波器,來去掉訊號的預加重與多處理等化作用。“使用預補償必須進行許多工作。”

Horowitz表示。“對於我們如何積極地 |

|

推動從邏輯到軟體的轉移,許多人將會感到訝異。” |

|

|

作者:麥利 |

|

|

|

|

選用適當的電路保護產品降低建購管理維修成本 |

|

|

妨礙隱私?新偵測技術可穿透衣物 |

|

|

量子力學將解開宇宙「暗能量」之謎? |

|

|

|

|

高性能Al2O3陶瓷基板和高热导率AlN陶瓷基板 |

|

|

|

高溫共燒陶瓷陶瓷電熱元件 |

|

|

返回更多... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|